seginfo Struct Reference

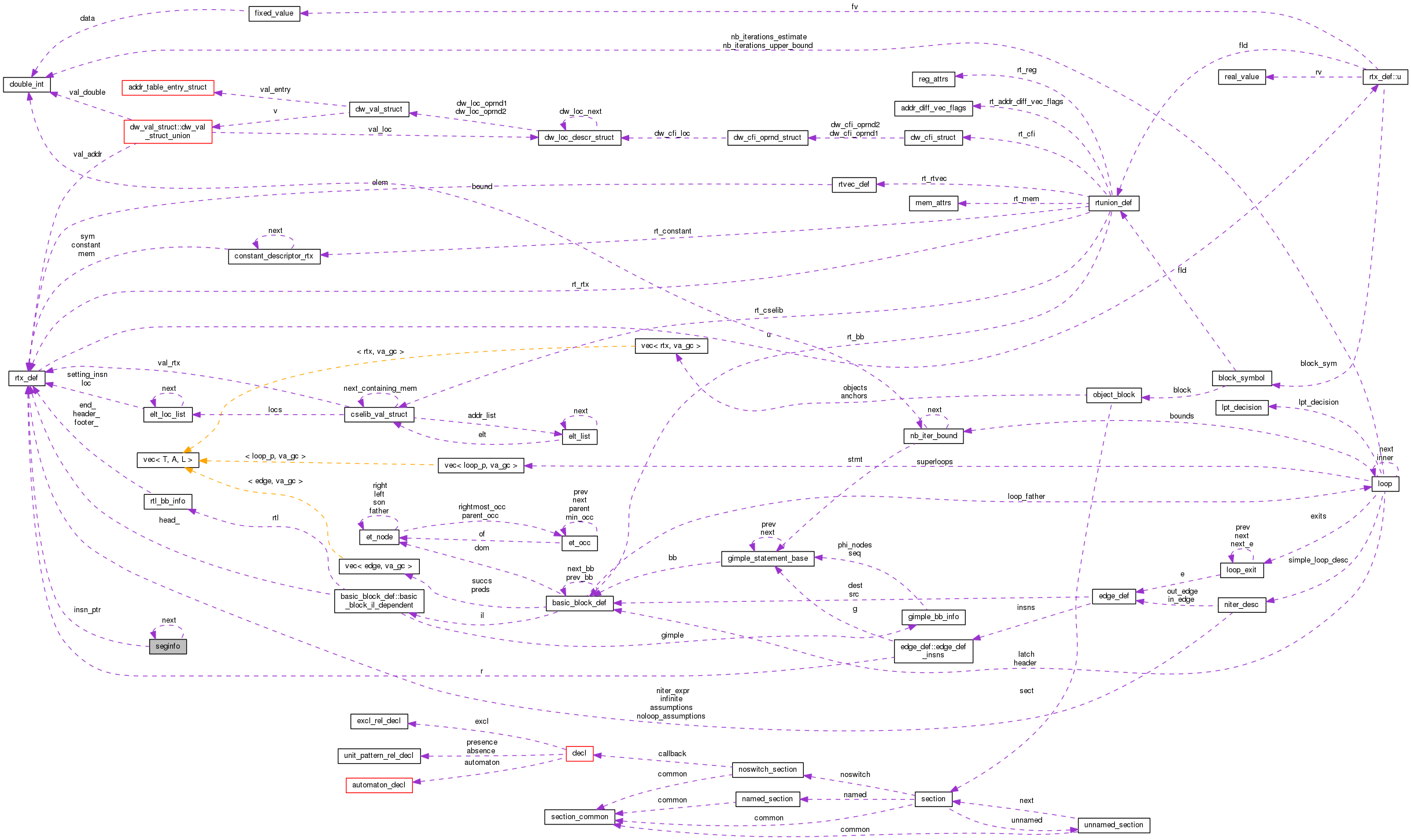

Collaboration diagram for seginfo:

Data Fields | |

| int | mode |

| rtx | insn_ptr |

| int | bbnum |

| struct seginfo * | next |

| HARD_REG_SET | regs_live |

Detailed Description

@verbatim

CPU mode switching Copyright (C) 1998-2013 Free Software Foundation, Inc.

This file is part of GCC.

GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version.

GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see http://www.gnu.org/licenses/.

We want target macros for the mode switching code to be able to refer to instruction attribute values.

The algorithm for setting the modes consists of scanning the insn list and finding all the insns which require a specific mode. Each insn gets a unique struct seginfo element. These structures are inserted into a list for each basic block. For each entity, there is an array of bb_info over the flow graph basic blocks (local var 'bb_info'), and contains a list of all insns within that basic block, in the order they are encountered. For each entity, any basic block WITHOUT any insns requiring a specific mode are given a single entry, without a mode. (Each basic block in the flow graph must have at least one entry in the segment table.) The LCM algorithm is then run over the flow graph to determine where to place the sets to the highest-priority value in respect of first the first insn in any one block. Any adjustments required to the transparency vectors are made, then the next iteration starts for the next-lower priority mode, till for each entity all modes are exhausted. More details are located in the code for optimize_mode_switching().

This structure contains the information for each insn which requires either single or double mode to be set. MODE is the mode this insn must be executed in. INSN_PTR is the insn to be executed (may be the note that marks the beginning of a basic block). BBNUM is the flow graph basic block this insn occurs in. NEXT is the next insn in the same basic block.

Field Documentation

| int seginfo::bbnum |

| rtx seginfo::insn_ptr |

| int seginfo::mode |

Referenced by create_pre_exit().

| struct seginfo* seginfo::next |

Referenced by add_seginfo().

| HARD_REG_SET seginfo::regs_live |

The documentation for this struct was generated from the following file: