#include <ira-int.h>

Public Member Functions |

| | HARD_REG_SET (x_ira_reg_mode_hard_regset[FIRST_PSEUDO_REGISTER][NUM_MACHINE_MODES]) |

Member Function Documentation

| target_ira_int::HARD_REG_SET |

( |

x_ira_reg_mode_hard_regset |

[FIRST_PSEUDO_REGISTER][NUM_MACHINE_MODES] | ) |

|

Map: hard regs X modes -> set of hard registers for storing value

of given mode starting with given hard register.

Field Documentation

| enum reg_class target_ira_int::x_alloc_reg_class_subclasses[N_REG_CLASSES][N_REG_CLASSES] |

For each reg class, table listing all the classes contained in it

(excluding the class itself. Non-allocatable registers are

excluded from the consideration).

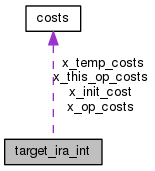

| struct costs* target_ira_int::x_init_cost |

Allocated and initialized once, and used to initialize cost values

for each insn.

| short target_ira_int::x_ira_class_hard_reg_index[N_REG_CLASSES][FIRST_PSEUDO_REGISTER] |

Index (in ira_class_hard_regs; for given register class and hard

register (in general case a hard register can belong to several

register classes;. The index is negative for hard registers

unavailable for the allocation.

| int target_ira_int::x_ira_important_class_nums[N_REG_CLASSES] |

The array containing indexes of important classes in the previous

array. The array elements are defined only for important

classes.

| enum reg_class target_ira_int::x_ira_important_classes[N_REG_CLASSES] |

The array containing all non-empty classes. Such classes is

important for calculation of the hard register usage costs.

| int target_ira_int::x_ira_important_classes_num |

The value is number of elements in the subsequent array.

| short int target_ira_int::x_ira_max_memory_move_cost[MAX_MACHINE_MODE][N_REG_CLASSES][2] |

Array analog of the macro MEMORY_MOVE_COST but they contain maximal

cost not minimal.

| move_table* target_ira_int::x_ira_may_move_in_cost[MAX_MACHINE_MODE] |

Similar, but here we don't have to move if the first index is a

subset of the second so in that case the cost is zero.

| move_table* target_ira_int::x_ira_may_move_out_cost[MAX_MACHINE_MODE] |

Similar, but here we don't have to move if the first index is a

superset of the second so in that case the cost is zero.

| short target_ira_int::x_ira_non_ordered_class_hard_regs[N_REG_CLASSES][FIRST_PSEUDO_REGISTER] |

Array of the number of hard registers of given class which are

available for allocation. The order is defined by the hard

register numbers.

| HARD_REG_SET target_ira_int::x_ira_prohibited_class_mode_regs[N_REG_CLASSES][NUM_MACHINE_MODES] |

Array whose values are hard regset of hard registers available for

the allocation of given register class whose HARD_REGNO_MODE_OK

values for given mode are zero.

| HARD_REG_SET target_ira_int::x_ira_prohibited_mode_move_regs[NUM_MACHINE_MODES] |

Array whose values are hard regset of hard registers for which

move of the hard register in given mode into itself is

prohibited.

| bool target_ira_int::x_ira_prohibited_mode_move_regs_initialized_p |

Flag of that the above array has been initialized.

| bool target_ira_int::x_ira_reg_allocno_class_p[N_REG_CLASSES] |

Map class->true if class is a possible allocno class, false

otherwise.

| enum reg_class target_ira_int::x_ira_reg_class_intersect[N_REG_CLASSES][N_REG_CLASSES] |

The biggest important class inside of intersection of the two

classes (that is calculated taking only hard registers available

for allocation into account;. If the both classes contain no hard

registers available for allocation, the value is calculated with

taking all hard-registers including fixed ones into account.

| enum reg_class target_ira_int::x_ira_reg_class_subunion[N_REG_CLASSES][N_REG_CLASSES] |

The biggest (smallest) important class inside of (covering) union

of the two classes (that is calculated taking only hard registers

available for allocation into account). If the both classes

contain no hard registers available for allocation, the value is

calculated with taking all hard-registers including fixed ones

into account. In other words, the value is the corresponding

reg_class_subunion (reg_class_superunion) value.

| enum reg_class target_ira_int::x_ira_reg_class_super_classes[N_REG_CLASSES][N_REG_CLASSES] |

Classes with end marker LIM_REG_CLASSES which are intersected with

given class (the first index). That includes given class itself.

This is calculated taking only hard registers available for

allocation into account.

| enum reg_class target_ira_int::x_ira_reg_class_superunion[N_REG_CLASSES][N_REG_CLASSES] |

| bool target_ira_int::x_ira_reg_pressure_class_p[N_REG_CLASSES] |

Map class->true if class is a pressure class, false otherwise.

| move_table* target_ira_int::x_ira_register_move_cost[MAX_MACHINE_MODE] |

Maximum cost of moving from a register in one class to a register

in another class. Based on TARGET_REGISTER_MOVE_COST.

| bool target_ira_int::x_ira_uniform_class_p[N_REG_CLASSES] |

Map class->true if class is an uniform class, false otherwise.

| HARD_REG_SET target_ira_int::x_ira_useful_class_mode_regs[N_REG_CLASSES][NUM_MACHINE_MODES] |

Index [CL][M] contains R if R appears somewhere in a register of the form:

(reg:M R'), R' not in x_ira_prohibited_class_mode_regs[CL][M]

For example, if:

- (reg:M 2) is valid and occupies two registers;

- register 2 belongs to CL; and

- register 3 belongs to the same pressure class as CL

then (reg:M 2) contributes to [CL][M] and registers 2 and 3 will be

in the set.

| int target_ira_int::x_last_mode_for_init_move_cost |

Keep track of the last mode we initialized move costs for.

| int target_ira_int::x_max_struct_costs_size |

Initialized once. It is a maximal possible size of the allocated

struct costs.

Hard registers that can not be used for the register allocator for

all functions of the current compilation unit.

| struct costs* target_ira_int::x_op_costs[MAX_RECOG_OPERANDS] |

Allocated once, and used for the cost calculation.

| struct costs* target_ira_int::x_temp_costs |

Allocated once, and used for temporary purposes.

| struct costs* target_ira_int::x_this_op_costs[MAX_RECOG_OPERANDS] |

The documentation for this struct was generated from the following file: