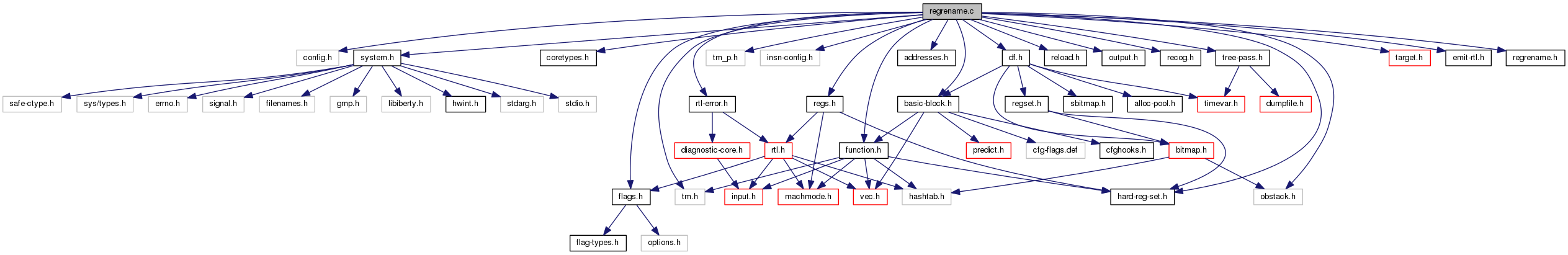

#include "config.h"#include "system.h"#include "coretypes.h"#include "tm.h"#include "rtl-error.h"#include "tm_p.h"#include "insn-config.h"#include "regs.h"#include "addresses.h"#include "hard-reg-set.h"#include "basic-block.h"#include "reload.h"#include "output.h"#include "function.h"#include "recog.h"#include "flags.h"#include "obstack.h"#include "tree-pass.h"#include "df.h"#include "target.h"#include "emit-rtl.h"#include "regrename.h"

Data Structures | |

| struct | incoming_reg_info |

| struct | bb_rename_info |

Enumerations | |

| enum | scan_actions { terminate_write, terminate_dead, mark_all_read, mark_read, mark_write, mark_access } |

Functions | |

| static void | scan_rtx (rtx, rtx *, enum reg_class, enum scan_actions, enum op_type) |

| static bool | build_def_use (basic_block) |

| du_head_p | regrename_chain_from_id () |

| static void | dump_def_use_chain () |

| static void | free_chain_data () |

| static void | mark_conflict () |

| static void | record_operand_use () |

| static du_head_p | create_new_chain (unsigned this_regno, unsigned this_nregs, rtx *loc, rtx insn, enum reg_class cl) |

| static void | merge_overlapping_regs () |

| static bool | check_new_reg_p (int reg, int new_reg, struct du_head *this_head, HARD_REG_SET this_unavailable) |

| int | find_best_rename_reg (du_head_p this_head, enum reg_class super_class, HARD_REG_SET *unavailable, int old_reg) |

| static void | rename_chains () |

| static void | init_rename_info () |

| static void | set_incoming_from_chain () |

| static void | merge_chains () |

| void | regrename_analyze () |

| void | regrename_do_replace () |

| static bool | verify_reg_in_set () |

| static bool | verify_reg_tracked () |

| static void | note_sets_clobbers () |

| static void | scan_rtx_reg (rtx insn, rtx *loc, enum reg_class cl, enum scan_actions action, enum op_type type) |

| static void | scan_rtx_address (rtx insn, rtx *loc, enum reg_class cl, enum scan_actions action, enum machine_mode mode, addr_space_t as) |

| static void | hide_operands (int n_ops, rtx *old_operands, rtx *old_dups, unsigned HOST_WIDE_INT do_not_hide, bool inout_and_ec_only) |

| static void | restore_operands () |

| static void | record_out_operands () |

| static bool | build_def_use () |

| void | regrename_init () |

| void | regrename_finish () |

| static unsigned int | regrename_optimize () |

| static bool | gate_handle_regrename () |

| rtl_opt_pass * | make_pass_regrename () |

Variables | |

| static const char *const | scan_actions_name [] |

| static int | tick [FIRST_PSEUDO_REGISTER] |

| static int | this_tick = 0 |

| static struct obstack | rename_obstack |

| vec< insn_rr_info > | insn_rr |

| static unsigned | current_id |

| static vec< du_head_p > | id_to_chain |

| static struct du_head * | open_chains |

| static bitmap_head | open_chains_set |

| static HARD_REG_SET | live_in_chains |

| static HARD_REG_SET | live_hard_regs |

| static operand_rr_info * | cur_operand |

| static bool | fail_current_block |

Enumeration Type Documentation

| enum scan_actions |

Register renaming for the GNU compiler. Copyright (C) 2000-2013 Free Software Foundation, Inc.

This file is part of GCC.

GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version.

GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see http://www.gnu.org/licenses/. This file implements the RTL register renaming pass of the compiler. It is a semi-local pass whose goal is to maximize the usage of the register file of the processor by substituting registers for others in the solution given by the register allocator. The algorithm is as follows:

- Local def/use chains are built: within each basic block, chains are opened and closed; if a chain isn't closed at the end of the block, it is dropped. We pre-open chains if we have already examined a predecessor block and found chains live at the end which match live registers at the start of the new block.

- We try to combine the local chains across basic block boundaries by comparing chains that were open at the start or end of a block to those in successor/predecessor blocks.

- For each chain, the set of possible renaming registers is computed. This takes into account the renaming of previously processed chains. Optionally, a preferred class is computed for the renaming register.

- The best renaming register is computed for the chain in the above set, using a round-robin allocation. If a preferred class exists, then the round-robin allocation is done within the class first, if possible. The round-robin allocation of renaming registers itself is global.

- If a renaming register has been found, it is substituted in the chain.

Targets can parameterize the pass by specifying a preferred class for the renaming register for a given (super)class of registers to be renamed.

Function Documentation

|

static |

|

static |

Build def/use chain.

Process the insn, determining its effect on the def-use

chains and live hard registers. We perform the following

steps with the register references in the insn, simulating

its effect:

(1) Deal with earlyclobber operands and CLOBBERs of non-operands

by creating chains and marking hard regs live.

(2) Any read outside an operand causes any chain it overlaps

with to be marked unrenamable.

(3) Any read inside an operand is added if there's already

an open chain for it.

(4) For any REG_DEAD note we find, close open chains that

overlap it.

(5) For any non-earlyclobber write we find, close open chains

that overlap it.

(6) For any non-earlyclobber write we find in an operand, make

a new chain or mark the hard register as live.

(7) For any REG_UNUSED, close any chains we just opened.

We cannot deal with situations where we track a reg in one mode

and see a reference in another mode; these will cause the chain

to be marked unrenamable or even cause us to abort the entire

basic block.

Simplify the code below by rewriting things to reflect

matching constraints. Also promote OP_OUT to OP_INOUT in

predicated instructions, but only for register operands

that are already tracked, so that we can create a chain

when the first SET makes a register live. A special case to deal with instruction patterns that

have matching operands with different modes. If we're

not already tracking such a reg, we won't start here,

and we must instead make sure to make the operand visible

to the machinery that tracks hard registers. If there's an in-out operand with a register that is not

being tracked at all yet, open a chain. Step 1a: Mark hard registers that are clobbered in this insn,

outside an operand, as live. Step 1b: Begin new chains for earlyclobbered writes inside

operands. Step 2: Mark chains for which we have reads outside operands

as unrenamable.

We do this by munging all operands into CC0, and closing

everything remaining. Step 2B: Can't rename function call argument registers.

Step 2C: Can't rename asm operands that were originally

hard registers. Step 3: Append to chains for reads inside operands.

Don't scan match_operand here, since we've no reg class

information to pass down. Any operands that we could

substitute in will be represented elsewhere. Step 3B: Record updates for regs in REG_INC notes, and

source regs in REG_FRAME_RELATED_EXPR notes. Step 4: Close chains for registers that die here, unless

the register is mentioned in a REG_UNUSED note. In that

case we keep the chain open until step #7 below to ensure

it conflicts with other output operands of this insn.

See PR 52573. Arguably the insn should not have both

notes; it has proven difficult to fix that without

other undesirable side effects. Step 4B: If this is a call, any chain live at this point

requires a caller-saved reg. Step 5: Close open chains that overlap writes. Similar to

step 2, we hide in-out operands, since we do not want to

close these chains. We also hide earlyclobber operands,

since we've opened chains for them in step 1, and earlier

chains they would overlap with must have been closed at

the previous insn at the latest, as such operands cannot

possibly overlap with any input operands. Step 6a: Mark hard registers that are set in this insn,

outside an operand, as live. Step 6b: Begin new chains for writes inside operands.

Step 6c: Record destination regs in REG_FRAME_RELATED_EXPR

notes for update. Step 7: Close chains for registers that were never

really used here.

References operand_alternative::cl, create_new_chain(), GET_MODE, GET_MODE_SIZE, hard_regno_nregs, live_in_chains, operand_alternative::matches, NULL_RTX, OP_INOUT, OP_OUT, recog_data_d::operand, recog_data_d::operand_mode, recog_data_d::operand_type, recog_data, recog_op_alt, REG_P, REGNO, verify_reg_in_set(), and verify_reg_tracked().

|

static |

Check if NEW_REG can be the candidate register to rename for REG in THIS_HEAD chain. THIS_UNAVAILABLE is a set of unavailable hard registers.

Can't use regs which aren't saved by the prologue.

See whether it accepts all modes that occur in definition and uses.

Referenced by find_best_rename_reg().

|

static |

Create a new chain for THIS_NREGS registers starting at THIS_REGNO, and record its occurrence in *LOC, which is being written to in INSN. This access requires a register of class CL.

Since we're tracking this as a chain now, remove it from the list of conflicting live hard registers and track it in live_in_chains instead.

Referenced by build_def_use().

|

static |

Dump all def/use chains, starting at id FROM.

| int find_best_rename_reg | ( | du_head_p | this_head, |

| enum reg_class | super_class, | ||

| HARD_REG_SET * | unavailable, | ||

| int | old_reg | ||

| ) |

For the chain THIS_HEAD, compute and return the best register to rename to. SUPER_CLASS is the superunion of register classes in the chain. UNAVAILABLE is a set of registers that cannot be used. OLD_REG is the register currently used for the chain.

Further narrow the set of registers we can use for renaming. If the chain needs a call-saved register, mark the call-used registers as unavailable.

Mark registers that overlap this chain's lifetime as unavailable.

Compute preferred rename class of super union of all the classes in the chain.

If PREFERRED_CLASS is not NO_REGS, we iterate in the first pass over registers that belong to PREFERRED_CLASS and try to find the best register within the class. If that failed, we iterate in the second pass over registers that don't belong to the class. If PREFERRED_CLASS is NO_REGS, we iterate over all registers in ascending order without any preference.

In the first pass, we force the renaming of registers that

don't belong to PREFERRED_CLASS to registers that do, even

though the latters were used not very long ago.

References check_new_reg_p(), reg_class_contents, TEST_HARD_REG_BIT, and tick.

|

static |

References bitmap_set_bit, du_head::conflicts, and du_head::next_chain.

|

static |

|

static |

Hide operands of the current insn (of which there are N_OPS) by substituting cc0 for them. Previous values are stored in the OLD_OPERANDS and OLD_DUPS. For every bit set in DO_NOT_HIDE, we leave the operand alone. If INOUT_AND_EC_ONLY is set, we only do this for OP_INOUT type operands and earlyclobbers.

Don't squash match_operator or match_parallel here, since we don't know that all of the contained registers are reachable by proper operands.

|

static |

Initialize a rename_info structure P for basic block BB, which starts a new scan.

Open chains based on information from (at least one) predecessor block. This gives us a chance later on to combine chains across basic block boundaries. Inconsistencies (in access sizes) will be caught normally and dealt with conservatively by disabling the chain for renaming, and there is no risk of losing optimization opportunities by opening chains either: if we did not open the chains, we'd have to track the live register as a hard reg, and we'd be unable to rename it in any case.

| rtl_opt_pass* make_pass_regrename | ( | ) |

|

static |

Walk all chains starting with CHAINS and record that they conflict with another chain whose id is ID.

|

static |

Merge the two chains C1 and C2 so that all conflict information is recorded and C1, and the id of C2 is changed to that of C1.

|

static |

For a def-use chain HEAD, find which registers overlap its lifetime and set the corresponding bits in *PSET.

References call_used_regs, crtl, df_regs_ever_live_p(), du_head::first, fixed_regs, GET_MODE, global_regs, hard_regno_nregs, du_chain::loc, and TEST_HARD_REG_BIT.

|

static |

Called through note_stores. DATA points to a rtx_code, either SET or CLOBBER, which tells us which kind of rtx to look at. If we have a match, record the set register in live_hard_regs and in the hard_conflicts bitmap of open chains.

There must not be pseudos at this point.

References du_head::cannot_rename, DEBUG_INSN_P, du_head::id, INSN_UID, reg_names, du_head::regno, and scan_actions_name.

|

static |

Examine cur_operand, and if it is nonnull, record information about the use THIS_DU which is part of the chain HEAD.

References bitmap_default_obstack, bitmap_initialize, du_head::cannot_rename, du_head::conflicts, current_id, du_head::id, du_head::need_caller_save_reg, du_head::next_chain, du_head::nregs, open_chains, du_head::regno, and rename_obstack.

|

static |

For each output operand of INSN, call scan_rtx to create a new open chain. Do this only for normal or earlyclobber outputs, depending on EARLYCLOBBER. If INSN_INFO is nonnull, use it to record information about the operands in the insn.

??? Many targets have output constraints on the SET_DEST of a call insn, which is stupid, since these are certainly ABI defined hard registers. For these, and for asm operands that originally referenced hard registers, we must record that the chain cannot be renamed.

| void regrename_analyze | ( | ) |

Analyze the current function and build chains for renaming.

Gather some information about the blocks in this function.

The order in which we visit blocks ensures that whenever possible, we only process a block after at least one of its predecessors, which provides a "seeding" effect to make the logic in set_incoming_from_chain and init_rename_info useful.

Add successor blocks to the worklist if necessary, and record

data about our own open chains at the end of this block, which

will be used to pre-open chains when processing the successors. Now, combine the chains data we have gathered across basic block boundaries. For every basic block, there may be chains open at the start, or at the end. Rather than exclude them from renaming, we look for open chains with matching registers at the other side of the CFG edge. For a given chain using register R, open at the start of block B, we must find an open chain using R on the other side of every edge leading to B, if the register is live across this edge. In the code below, N_PREDS_USED counts the number of edges where the register is live, and N_PREDS_JOINED counts those where we found an appropriate chain for joining. We perform the analysis for both incoming and outgoing edges, but we only need to merge once (in the second part, after verifying outgoing edges).

| du_head_p regrename_chain_from_id | ( | ) |

Return the chain corresponding to id number ID. Take into account that chains may have been merged.

References dump_file, du_head::first, FOR_EACH_VEC_ELT_FROM, du_chain::insn, INSN_UID, du_head::nregs, reg_class_names, reg_names, and du_head::regno.

| void regrename_do_replace | ( | ) |

| void regrename_finish | ( | void | ) |

Free all global data used by the register renamer.

| void regrename_init | ( | ) |

Initialize the register renamer. If INSN_INFO is true, ensure that insn_rr is nonnull.

|

static |

Perform register renaming on the current function.

|

static |

Perform register renaming on the current function.

Don't clobber traceback for noreturn functions.

Iterate over elements in the chain in order to:

1. Count number of uses, and narrow the set of registers we can

use for renaming.

2. Compute the superunion of register classes in this chain.

|

static |

Undo the substitution performed by hide_operands. INSN is the insn we are processing; the arguments are the same as in hide_operands.

References BB_HEAD, HOST_WIDE_INT, NEXT_INSN, NONDEBUG_INSN_P, and SET.

|

static |

Should only happen inside MEM.

|

static |

Adapted from find_reloads_address_1. CL is INDEX_REG_CLASS or BASE_REG_CLASS depending on how the register is being considered.

If the target doesn't claim to handle autoinc, this must be something special, like a stack push. Kill this chain.

|

static |

??? Class NO_REGS can happen if the md file makes use of

EXTRA_CONSTRAINTS to match registers. Which is arguably

wrong, but there we are.

Avoid adding the same location in a DEBUG_INSN multiple times,

which could happen with non-exact overlap. Otherwise, find any other chains that do not match exactly;

ensure they all get marked unrenamable. Whether the terminated chain can be used for renaming

depends on the action and this being an exact match.

In either case, we remove this element from open_chains. In this case, tracking liveness gets too hard. Fail the

entire basic block.

|

static |

Record in RI that the block corresponding to it has an incoming live value, described by CHAIN.

If we've recorded the same information before, everything is fine.

If we have no information for any of the involved registers, update the incoming array.

There must be some kind of conflict. Prevent both the old and new ranges from being used.

References bitmap_ior_into(), du_head::cannot_rename, du_head::conflicts, du_head::first, du_head::hard_conflicts, du_head::id, IOR_HARD_REG_SET, du_head::last, du_head::need_caller_save_reg, du_chain::next_use, and NULL.

|

static |

Return true if OP is a reg for which all bits are set in PSET, false if all bits are clear. In other cases, set fail_current_block and return false.

Referenced by build_def_use().

|

static |

Return true if OP is a reg that is being tracked already in some form. May set fail_current_block if it sees an unhandled case of overlap.

References du_head::next_chain.

Referenced by build_def_use().

Variable Documentation

|

static |

Set while scanning RTL if INSN_RR is nonnull, i.e. if the current analysis is for a caller that requires operand data. Used in record_operand_use.

|

static |

The id to be given to the next opened chain.

Referenced by record_operand_use().

|

static |

True if we found a register with a size mismatch, which means that we can't track its lifetime accurately. If so, we abort the current block without renaming.

| vec<insn_rr_info> insn_rr |

If nonnull, the code calling into the register renamer requested information about insn operands, and we store it here.

|

static |

Record the registers that are live but not tracked. The intersection between this and live_in_chains is empty.

|

static |

Record the registers being tracked in open_chains.

Referenced by build_def_use().

|

static |

List of currently open chains.

Referenced by record_operand_use().

|

static |

Bitmap of open chains. The bits set always match the list found in open_chains.

|

static |

Referenced by record_operand_use().

|

static |

Referenced by note_sets_clobbers().

|

static |

|

static |

TICK and THIS_TICK are used to record the last time we saw each register.

Referenced by dfs_next_edge(), and find_best_rename_reg().