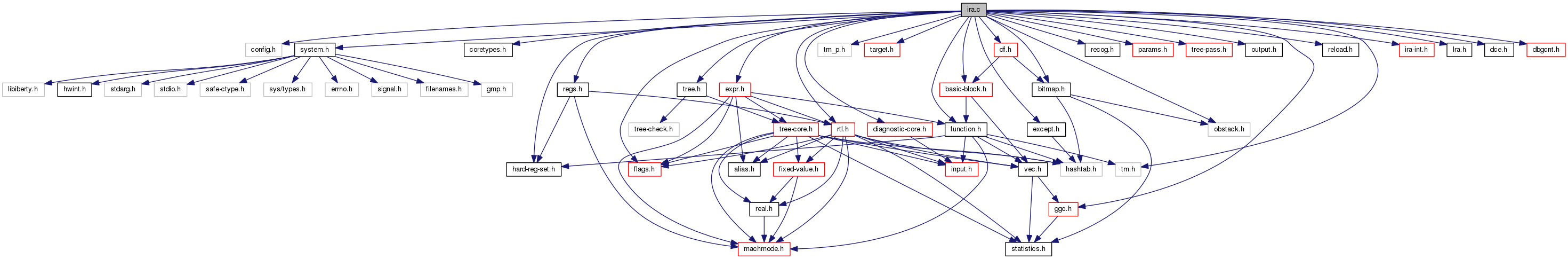

#include "config.h"#include "system.h"#include "coretypes.h"#include "tm.h"#include "regs.h"#include "tree.h"#include "rtl.h"#include "tm_p.h"#include "target.h"#include "flags.h"#include "obstack.h"#include "bitmap.h"#include "hard-reg-set.h"#include "basic-block.h"#include "df.h"#include "expr.h"#include "recog.h"#include "params.h"#include "tree-pass.h"#include "output.h"#include "except.h"#include "reload.h"#include "diagnostic-core.h"#include "function.h"#include "ggc.h"#include "ira-int.h"#include "lra.h"#include "dce.h"#include "dbgcnt.h"

Data Structures | |

| struct | equivalence |

Macros | |

| #define | last_mode_for_init_move_cost (this_target_ira_int->x_last_mode_for_init_move_cost) |

| #define | no_unit_alloc_regs (this_target_ira_int->x_no_unit_alloc_regs) |

| #define | alloc_reg_class_subclasses (this_target_ira_int->x_alloc_reg_class_subclasses) |

| #define | IRA_NO_OBSTACK |

| #define | ira_prohibited_mode_move_regs_initialized_p (this_target_ira_int->x_ira_prohibited_mode_move_regs_initialized_p) |

Macro Definition Documentation

| #define alloc_reg_class_subclasses (this_target_ira_int->x_alloc_reg_class_subclasses) |

Referenced by setup_alloc_regs(), and setup_stack_reg_pressure_class().

| #define IRA_NO_OBSTACK |

Define the following macro if allocation through malloc if preferable.

| #define ira_prohibited_mode_move_regs_initialized_p (this_target_ira_int->x_ira_prohibited_mode_move_regs_initialized_p) |

Referenced by ira_init_once().

| #define last_mode_for_init_move_cost (this_target_ira_int->x_last_mode_for_init_move_cost) |

Referenced by clarify_prohibited_class_mode_regs().

| #define no_unit_alloc_regs (this_target_ira_int->x_no_unit_alloc_regs) |

Function Documentation

|

static |

In DEBUG_INSN location adjust REGs from CLEARED_REGS bitmap to the equivalent replacement.

|

static |

If the backend knows where to allocate pseudos for hard register initial values, register these allocations now.

Poke the regno right into regno_reg_rtx so that even fixed regs are accepted.

Update global register liveness information.

|

static |

Walk the insns of the current function and build reload_insn_chain, and record register life information.

live_subregs is a vector used to keep accurate information about which hardregs are live in multiword pseudos. live_subregs and live_subregs_used are indexed by pseudo number. The live_subreg entry for a particular pseudo is only used if the corresponding element is non zero in live_subregs_used. The sbitmap size of live_subreg[allocno] is number of bytes that the pseudo can occupy.

Ignore may clobbers because these are generated

from calls. However, every other kind of def is

added to dead_or_set. We can model subregs, but not if they are

wrapped in ZERO_EXTRACTS. Expand the range to cover entire words.

Bytes added here are "don't care". Ignore the paradoxical bits.

Set live_relevant_regs here because

that bit has to be true to get us to

look at the live_subregs fields. DF_REF_PARTIAL is generated for

subregs, STRICT_LOW_PART, and

ZERO_EXTRACT. We handle the subreg

case above so here we have to keep from

modeling the def as a killing def. DF_REF_READ_WRITE on a use means that this use

is fabricated from a def that is a partial set

to a multiword reg. Here, we only model the

subreg case that is not wrapped in ZERO_EXTRACT

precisely so we do not need to look at the

fabricated use. Add the last use of each var to dead_or_set.

Ignore the paradoxical bits.

Resetting the live_subregs_used is

effectively saying do not use the subregs

because we are reading the whole

pseudo. FIXME!! The following code is a disaster. Reload needs to see the

labels and jump tables that are just hanging out in between

the basic blocks. See pr33676. Skip over the barriers and cruft.

While we add anything except barriers and notes, the focus is

to get the labels and jump tables into the

reload_insn_chain. The block makes no sense here, but it is what the old

code did.

|

static |

Evaluate overall allocation cost and the costs for using hard registers and memory for allocnos.

References ira_reg_equiv::init_insns, max_reg_num(), max_regno, and reg_equiv_init.

|

static |

Clarify IRA_PROHIBITED_CLASS_MODE_REGS by excluding hard registers spanning from one register pressure class to another one. It is called after defining the pressure classes.

References ira_may_move_in_cost, ira_may_move_out_cost, ira_register_move_cost, and last_mode_for_init_move_cost.

|

static |

Return TRUE if the operand constraint STR is commutative.

Usually `' is the first constraint character but the documentation does not require this.

References recog_data_d::n_alternatives, recog_data_d::operand, and recog_data.

|

static |

The function used to sort the important classes.

|

static |

Add register clobbers from asm statements.

|

static |

TRUE if X uses any registers for which reg_equiv[REGNO].replace is true.

References find_reg_note(), NULL_RTX, remove_note(), and XEXP.

|

static |

Search forward to see if the source register of a copy insn dies before either it or the destination register is modified, but don't scan past the end of the basic block. If so, we can replace the source with the destination and let the source die in the copy insn.

This will reduce the number of registers live in that range and may enable the destination and the source coalescing, thus often saving one register in addition to a register-register copy.

We don't want to mess with hard regs if register classes

are small.

We don't see all updates to SP if they are in an

auto-inc memory reference, so we must disallow this

optimization on them. If SRC is an asm-declared register, it must not be

replaced in any asm. Unfortunately, the REG_EXPR

tree for the asm variable may be absent in the SRC

rtx, so we can't check the actual register

declaration easily (the asm operand will have it,

though). To avoid complicating the test for a rare

case, we just don't perform register replacement

for a hard reg mentioned in an asm. Don't change hard registers used by a call.

Don't change a USE of a register.

See if all of SRC dies in P. This test is slightly

more conservative than it needs to be. We can do the optimization. Scan forward from INSN

again, replacing regs as we go. Set FAILED if a

replacement can't be done. In that case, we can't

move the death note for SRC. This should be

rare. Set to stop at next insn.

If SRC is a hard register, we might miss

some overlapping registers with

validate_replace_rtx, so we would have to

undo it. We can't if DEST is present in

the insn, so fail in that combination of

cases. Attempt to replace all uses.

If this succeeded, but some part of the

register is still present, undo the

replacement. If DEST dies here, remove the death note and

save it for later. Make sure ALL of DEST dies

here; again, this is overly conservative. Move death note of SRC from P to INSN.

DEST is also dead if INSN has a REG_UNUSED note for

DEST. Put death note of DEST on P if we saw it die.

If SRC is a hard register which is set or killed in

some other way, we can't do this optimization.

References PATTERN, reg_mentioned_p(), reg_overlap_mentioned_p(), and validate_replace_rtx().

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

???!!! Move it before lra () when we use ira_reg_equiv in LRA.

The code after the reload has changed so much that at this point we might as well just rescan everything. Note that df_rescan_all_insns is not going to help here because it does not touch the artificial uses and defs.

|

static |

Returns nonzero if X (used to initialize register REGNO) is movable. X is only movable if the registers it uses have equivalent initializations which appear to be within the same loop (or in an inner loop) and movable or if they are not candidates for local_alloc and don't vary.

Fall through.

|

static |

Returns zero if X is known to be invariant.

Fall through.

References CASE_CONST_ANY, GET_CODE, GET_RTX_FORMAT, GET_RTX_LENGTH, MEM_P, memref_referenced_p(), REGNO, SET, SET_DEST, SET_SRC, true_dependence(), and XEXP.

Referenced by finish_reg_equiv().

|

static |

Regional allocation can create new pseudo-registers. This function expands some arrays for pseudo-registers.

References anti_dependence(), MEM_P, reg_overlap_mentioned_p(), and REG_P.

Referenced by move_unallocated_pseudos().

|

static |

Look for instances where we have an instruction that is known to increase register pressure, and whose result is not used immediately. If it is possible to move the instruction downwards to just before its first use, split its lifetime into two ranges. We create a new pseudo to compute the value, and emit a move instruction just before the first use. If, after register allocation, the new pseudo remains unallocated, the function move_unallocated_pseudos then deletes the move instruction and places the computation just before the first use.

Such a move is safe and profitable if all the input registers remain live and unchanged between the original computation and its first use. In such a situation, the computation is known to increase register pressure, and moving it is known to at least not worsen it.

We restrict moves to only those cases where a register remains unallocated, in order to avoid interfering too much with the instruction schedule. As an exception, we may move insns which only modify their input register (typically induction variables), as this increases the freedom for our intended transformation, and does not limit the second instruction scheduler pass.

A set of registers which are live but not modified throughout a block.

A set of registers which only exist in a given basic block.

A set of registers which are set once, in an instruction that can be moved freely downwards, but are otherwise transparent to a block.

There must be exactly one def in this insn.

This must be the only definition of the reg. We also limit

which modes we deal with so that we can assume we can generate

move instructions.

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

Set up different arrays concerning class subsets, allocno and important classes.

References AND_COMPL_HARD_REG_SET, COPY_HARD_REG_SET, count, no_unit_alloc_regs, reg_class_contents, and temp_hard_regset.

|

static |

References equiv_init_varies_p(), XVECEXP, and XVECLEN.

|

static |

Fix values of array REG_EQUIV_INIT after live range splitting done by IRA.

Remove the wrong list element.

References ira_loop_tree_root, ira_pressure_classes, and ira_loop_tree_node::reg_pressure.

|

static |

Free ira_max_register_move_cost, ira_may_move_in_cost and ira_may_move_out_cost for each mode.

Reset move_cost and friends, making sure we only free shared table entries once.

|

static |

Init LIVE_SUBREGS[ALLOCNUM] and LIVE_SUBREGS_USED[ALLOCNUM] using REG to the number of nregs, and INIT_VALUE to get the initialization. ALLOCNUM need not be the regno of REG.

Been there, done that.

Create a new one.

If the entire reg was live before blasting into subregs, we need to init all of the subregs to ones else init to 0.

Referenced by setup_reg_equiv().

|

static |

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

Return TRUE if INSN contains an ASM.

References eliminable_regset, frame_pointer_needed, ira_no_alloc_regs, and SET_HARD_REG_BIT.

|

static |

Return TRUE if *LOC contains an asm.

References eliminable_regset, frame_pointer_needed, HARD_FRAME_POINTER_REGNUM, ira_no_alloc_regs, and SET_HARD_REG_BIT.

|

static |

A wrapper around dominated_by_p, which uses the information in UID_LUID to give dominance relationships between two insns I1 and I2.

|

static |

If insn is interesting for parameter range-splitting shring-wrapping preparation, i.e. it is a single set from a hard register to a pseudo, which is live at CALL_DOM, return the destination. Otherwise return NULL.

|

static |

This is the main entry of IRA.

If there are too many pseudos and/or basic blocks (e.g. 10K pseudos and 10K blocks or 100K pseudos and 1K blocks), we will use simplified and faster algorithms in LRA.

It permits to skip live range splitting in LRA.

There is no sense to do regional allocation when we use

simplified LRA. DF_LIVE can't be used in the register allocator, too many other parts of the compiler depend on using the "classic" liveness interpretation of the DF_LR problem. See PR38711. Remove the problem, so that we don't spend time updating it in any of the df_analyze() calls during IRA/LRA.

If we are not optimizing, then this is the only place before register allocation where dataflow is done. And that is needed to generate these warnings.

Determine if the current function is a leaf before running IRA since this can impact optimizations done by the prologue and epilogue thus changing register elimination offsets.

It is not worth to do such improvement when we use a simple allocation because of -O0 usage or because the function is too big.

It is just wasting compiler's time to pack spilled pseudos into stack slots in this case – prohibit it. We also do this if there is setjmp call because a variable not modified between setjmp and longjmp the compiler is required to preserve its value and sharing slots does not guarantee it.

New insns were generated: add notes and recalculate live

info. ??? Rebuild the loop tree, but why? Does the loop tree

change if new insns were generated? Can that be handled

by updating the loop tree incrementally? See comment for find_moveable_pseudos call.

Restore original values.

| void* ira_allocate | ( | ) |

Allocate memory of size LEN for IRA data.

| bitmap ira_allocate_bitmap | ( | void | ) |

Allocate and returns bitmap for IRA.

Referenced by coalesced_pseudo_reg_slot_compare(), do_coloring(), and ira_reuse_stack_slot().

| bool ira_bad_reload_regno | ( | ) |

Return nonzero if REGNO is a particularly bad choice for reloading IN or OUT.

|

static |

Return nonzero if REGNO is a particularly bad choice for reloading X.

We only deal with pseudo regs.

If the pseudo prefers REGNO explicitly, then do not consider REGNO a bad spill choice.

If the pseudo conflicts with REGNO, then we consider REGNO a poor choice for a reload regno.

References targetm.

| void ira_debug_allocno_classes | ( | void | ) |

Output all possible allocno and translation classes and the translation maps into stderr.

References targetm.

| void ira_debug_disposition | ( | void | ) |

Outputs information about allocation of all allocnos into stderr.

References AND_HARD_REG_SET, COPY_HARD_REG_SET, hard_reg_set_size(), ira_pressure_classes, ira_stack_reg_pressure_class, reg_class_contents, and temp_hard_regset.

| void ira_expand_reg_equiv | ( | void | ) |

Expand ira_reg_equiv if necessary.

| void ira_finish_once | ( | void | ) |

Function called once at the end of compiler work.

Referenced by lang_dependent_init_target().

| void ira_free | ( | ) |

Free memory ADDR allocated for IRA data.

| void ira_free_bitmap | ( | ) |

Free bitmap B allocated for IRA.

do nothing

| int ira_get_dup_out_num | ( | ) |

Return the number of the output non-early clobber operand which should be the same in any case as operand with number OP_NUM (or negative value if there is no such operand). The function takes only really possible alternatives into consideration.

We should find duplications only for input operands.

It is better ignore an alternative with early clobber.

| void ira_init | ( | void | ) |

This is called every time when register related information is changed.

References recog_data_d::alternative_enabled_p, and recog_data.

| void ira_init_once | ( | void | ) |

This is called once during compiler work. It sets up different arrays whose values don't depend on the compiled function.

References gen_rtx_REG(), and ira_prohibited_mode_move_regs_initialized_p.

| void ira_init_register_move_cost | ( | ) |

Allocate and initialize IRA_REGISTER_MOVE_COST, IRA_MAY_MOVE_IN_COST and IRA_MAY_MOVE_OUT_COST for MODE.

| void ira_print_disposition | ( | ) |

Output information about allocation of all allocnos (except for caps) into file F.

| void ira_setup_alts | ( | ) |

Setup possible alternatives in ALTS for INSN.

MAP nalt * nop -> start of constraints for given operand and alternative

Check that the hard reg set is enough for holding all alternatives. It is hard to imagine the situation when the assertion is wrong.

Calculate some data common for all alternatives to speed up the

function. We only support one commutative marker, the

first one. We already set commutative

above.

| void ira_setup_eliminable_regset | ( | ) |

Set up ELIMINABLE_REGSET, IRA_NO_ALLOC_REGS, and REGS_EVER_LIVE. If the function is called from IRA (not from the insn scheduler or RTL loop invariant motion), FROM_IRA_P is true.

FIXME: If EXIT_IGNORE_STACK is set, we will not save and restore sp for alloca. So we can't eliminate the frame pointer in that case. At some point, we should improve this by emitting the sp-adjusting insns for this case.

We need the frame pointer to catch stack overflow exceptions

if the stack pointer is moving. We need a frame pointer for all Cilk Plus functions that use

Cilk keywords. It can change FRAME_POINTER_NEEDED. We call it only from IRA because it is expensive.

Build the regset of all eliminable registers and show we can't use those that we already know won't be eliminated.

Referenced by split_live_ranges_for_shrink_wrap().

| void ira_update_equiv_info_by_shuffle_insn | ( | ) |

Update equiv regno from movement of FROM_REGNO to TO_REGNO. INSNS are insns which were generated for such movement. It is assumed that FROM_REGNO and TO_REGNO always have the same value at the point of any move containing such registers. This function is used to update equiv info for register shuffles on the region borders and for caller save/restore insns.

It is possible that FROM_REGNO still has no equivalence because in shuffles to_regno<-from_regno and from_regno<-to_regno the 2nd insn was not processed yet.

We don't add the insn to insn init list because memory

equivalence is just to say what memory is better to use

when the pseudo is spilled.

| rtl_opt_pass* make_pass_ira | ( | ) |

| rtl_opt_pass* make_pass_reload | ( | ) |

| void mark_elimination | ( | ) |

Indicate that hard register number FROM was eliminated and replaced with an offset from hard register number TO. The status of hard registers live at the start of a basic block is updated by replacing a use of FROM with a use of TO.

|

static |

TRUE if X references a memory location that would be affected by a store to MEMREF.

If we are setting a MEM, it doesn't count (its address does), but any other SET_DEST that has a MEM in it is referencing the MEM.

References BB_END, BB_HEAD, bb_loop_depth(), FOR_BB_INSNS, FOR_EACH_BB, for_each_rtx(), grow_reg_equivs(), init_alias_analysis(), INSN_P, loop_depth(), NEXT_INSN, no_equiv(), NONDEBUG_INSN_P, NULL, REG_NOTE_KIND, REG_NOTES, set_paradoxical_subreg(), single_set, and XEXP.

Referenced by equiv_init_varies_p().

|

static |

TRUE if some insn in the range (START, END] references a memory location that would be affected by a store to MEMREF.

Nonconst functions may access memory.

References no_equiv(), note_stores(), NULL, and PATTERN.

|

static |

Perform the second half of the transformation started in find_moveable_pseudos. We look for instances where the newly introduced pseudo remains unallocated, and remove it by moving the definition to just before its use, replacing the move instruction generated by find_moveable_pseudos.

The use must follow all definitions of OTHER_REG, so we can insert the new definition immediately after any of them.

References ALLOCNO_EMIT_DATA, ALLOCNO_REGNO, AVOID_CFG_MODIFICATIONS, CDI_DOMINATORS, df_analyze(), expand_reg_info(), FOR_EACH_ALLOCNO, free_dominance_info(), internal_flag_ira_verbose, ira_dump_file, ira_flattening(), ira_initiate_assign(), ira_reassign_conflict_allocnos(), loop_optimizer_finalize(), loop_optimizer_init(), LOOPS_HAVE_RECORDED_EXITS, max_regno_before_ira, NULL, REGNO, and setup_allocno_assignment_flags().

Mark REG as having no known equivalence. Some instructions might have been processed before and furnished with REG_EQUIV notes for this register; these notes will have to be removed. STORE is the piece of RTL that does the non-constant / conflicting assignment - a SET, CLOBBER or REG_INC note. It is currently not used, but needs to be there because this function is called from note_stores.

This doesn't matter for equivalences made for argument registers, we should keep their initialization insns.

Referenced by memref_referenced_p(), memref_used_between_p(), and set_paradoxical_subreg().

|

static |

Print chain C to FILE.

|

static |

Print all reload_insn_chains to FILE.

References bitmap_set_bit, fixed_regs, and pseudo_for_reload_consideration_p().

|

static |

Output all possible allocno or pressure classes and their translation map into file F.

References ira_allocno_classes, ira_class_hard_reg_index, and ira_hard_regno_allocno_class.

|

static |

Output all unifrom and important classes into file F.

References ira_allocno_class_translate, ira_allocno_classes_num, ira_hard_regno_allocno_class, no_unit_alloc_regs, and TEST_HARD_REG_BIT.

|

static |

Return true if pseudo REGNO should be added to set live_throughout or dead_or_set of the insn chains for reload consideration.

Consider spilled pseudos too for IRA because they still have a chance to get hard-registers in the reload when IRA is used.

Referenced by print_insn_chains(), and setup_reg_equiv().

|

static |

For correct work of function setup_reg_class_relation we need to reorder important classes according to the order of their allocno classes. It places important classes containing the same allocatable hard register set adjacent to each other and allocno class with the allocatable hard register set right after the other important classes with the same set.

In example from comments of function setup_allocno_and_important_classes, it places LEGACY_REGS and GENERAL_REGS close to each other and GENERAL_REGS is after LEGACY_REGS.

|

static |

Run the integrated register allocator.

|

static |

|

static |

Examine the rtx found in *LOC, which is read or written to as determined by TYPE. Return false if we find a reason why an insn containing this rtx should not be moved (such as accesses to non-constant memory), true otherwise.

References bitmap_set_bit, and dump_file.

|

static |

Check whether the SUBREG is a paradoxical subreg and set the result in PDX_SUBREGS.

References no_equiv(), note_stores(), NULL, and targetm.

Referenced by memref_referenced_p().

|

static |

Set up global variables defining info about hard registers for the allocation. These depend on USE_HARD_FRAME_P whose TRUE value means that we can use the hard frame pointer for the allocation.

References alloc_reg_class_subclasses, and HARD_REG_SET.

|

static |

Set up IRA_ALLOCNO_CLASSES, IRA_ALLOCNO_CLASSES_NUM, IRA_IMPORTANT_CLASSES, and IRA_IMPORTANT_CLASSES_NUM.

Target may have many subtargets and not all target hard regiters can be used for allocation, e.g. x86 port in 32-bit mode can not use hard registers introduced in x86-64 like r8-r15). Some classes might have the same allocatable hard registers, e.g. INDEX_REGS and GENERAL_REGS in x86 port in 32-bit mode. To decrease different calculations efforts we introduce allocno classes which contain unique non-empty sets of allocatable hard-registers.

Pseudo class cost calculation in ira-costs.c is very expensive. Therefore we are trying to decrease number of classes involved in such calculation. Register classes used in the cost calculation are called important classes. They are allocno classes and other non-empty classes whose allocatable hard register sets are inside of an allocno class hard register set. From the first sight, it looks like that they are just allocno classes. It is not true. In example of x86-port in 32-bit mode, allocno classes will contain GENERAL_REGS but not LEGACY_REGS (because allocatable hard registers are the same for the both classes). The important classes will contain GENERAL_REGS and LEGACY_REGS. It is done because a machine description insn constraint may refers for LEGACY_REGS and code in ira-costs.c is mostly base on investigation of the insn constraints.

Collect classes which contain unique sets of allocatable hard registers. Prefer GENERAL_REGS to other classes containing the same set of hard registers.

Prefer general regs. For i386 example, it means that

we prefer GENERAL_REGS over INDEX_REGS or LEGACY_REGS

(all of them consists of the same available hard

registers). Set up classes which can be used for allocnos as classes conatining non-empty unique sets of allocatable hard registers.

Add non-allocno classes containing to non-empty set of allocatable hard regs.

Now add allocno classes to the important classes.

References AND_COMPL_HARD_REG_SET, COPY_HARD_REG_SET, hard_reg_set_subset_p(), ira_allocno_classes, ira_allocno_classes_num, ira_important_classes, ira_important_classes_num, no_unit_alloc_regs, reg_class_contents, and temp_hard_regset.

|

static |

Set up allocno assignment flags for further allocation improvements.

It can happen if A is not referenced but partially anticipated somewhere in a region.

Don't assign hard registers to allocnos which are destination

of removed store at the end of loop. It has no sense to keep

the same value in different hard registers. It is also

impossible to assign hard registers correctly to such

allocnos because the cost info and info about intersected

calls are incorrect for them.

References ALLOCNO_HARD_REGNO, ALLOCNO_MODE, ALLOCNO_NUM_OBJECTS, ALLOCNO_REGNO, gcc_unreachable, hard_regno_nregs, OBJECT_ALLOCNO, OBJECT_SUBWORD, and REG_WORDS_BIG_ENDIAN.

Referenced by move_unallocated_pseudos().

|

static |

The function sets up the three arrays declared above.

References ira_class_hard_reg_index, and ira_non_ordered_class_hard_regs.

|

static |

Set up IRA_MEMORY_MOVE_COST and IRA_MAX_MEMORY_MOVE_COST.

Costs for NO_REGS are used in cost calculation on the 1st pass when the preferred register classes are not known yet. In this case we take the best scenario.

|

static |

Set up array IRA_ALLOCNO_CLASS_TRANSLATE and IRA_PRESSURE_CLASS_TRANSLATE.

|

static |

Setup translation in CLASS_TRANSLATE of all classes into a class given by array CLASSES of length CLASSES_NUM. The function is used make translation any reg class to an allocno class or to an pressure class. This translation is necessary for some calculations when we can use only allocno or pressure classes and such translation represents an approximate representation of all classes.

The translation in case when allocatable hard register set of a given class is subset of allocatable hard register set of a class in CLASSES is pretty simple. We use smallest classes from CLASSES containing a given class. If allocatable hard register set of a given class is not a subset of any corresponding set of a class from CLASSES, we use the cheapest (with load/store point of view) class from CLASSES whose set intersects with given class set

For classes which are not fully covered by one of given classes (in other words covered by more one given class), use the cheapest class.

|

static |

Set up the array above.

References CLEAR_HARD_REG_SET, in_hard_reg_set_p(), ira_class_hard_regs, ira_class_hard_regs_num, ira_class_singleton, ira_prohibited_class_mode_regs, SET_HARD_REG_BIT, and temp_hard_regset.

|

static |

Setup preferred and alternative classes for new pseudo-registers created by IRA starting with START.

|

static |

Find pressure classes which are register classes for which we calculate register pressure in IRA, register pressure sensitive insn scheduling, and register pressure sensitive loop invariant motion.

To make register pressure calculation easy, we always use non-intersected register pressure classes. A move of hard registers from one register pressure class is not more expensive than load and store of the hard registers. Most likely an allocno class will be a subset of a register pressure class and in many cases a register pressure class. That makes usage of register pressure classes a good approximation to find a high register pressure.

A register class without subclasses may contain a few

hard registers and movement between them is costly

(e.g. SPARC FPCC registers). We still should consider it

as a candidate for a pressure class.

Check that the moves between any hard registers of the

current class are not more expensive for a legal mode

than load/store of the hard registers of the current

class. Such class is a potential candidate to be a

register pressure class. Remove so far added pressure classes which are subset of the

current candidate class. Prefer GENERAL_REGS as a pressure

register class to another class containing the same

allocatable hard registers. We do this because machine

dependent cost hooks might give wrong costs for the latter

class but always give the right cost for the former class

(GENERAL_REGS). If the current candidate is a subset of a so far added

pressure class, don't add it to the list of the pressure

classes.

|

static |

Set up IRA_PROHIBITED_CLASS_MODE_REGS and IRA_CLASS_SINGLETON. This function is called once IRA_CLASS_HARD_REGS has been initialized.

|

static |

Set up IRA_PROHIBITED_MODE_MOVE_REGS.

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

Form IRA_REG_CLASS_MAX_NREGS and IRA_REG_CLASS_MIN_NREGS maps.

References CLEAR_HARD_REG_SET, hard_regno_nregs, ira_class_hard_regs, ira_class_hard_regs_num, ira_pressure_class_translate, ira_prohibited_class_mode_regs, ira_useful_class_mode_regs, SET_HARD_REG_BIT, and TEST_HARD_REG_BIT.

|

static |

Set up IRA_REG_CLASS_SUBUNION, IRA_REG_CLASS_SUPERUNION, IRA_REG_CLASS_SUPER_CLASSES, IRA_REG_CLASSES_INTERSECT, and IRA_REG_CLASSES_INTERSECT_P. For the meaning of the relations, please see corresponding comments in ira-int.h.

The both classes have no allocatable hard registers

– take all class hard registers into account and use

reg_class_subunion and reg_class_superunion.

CL1 and CL2 are important classes and CL1 allocatable

hard register set is inside of CL2 allocatable hard

registers – make CL1 a superset of CL2. CL3 allocatable hard register set is inside of

intersection of allocatable hard register sets

of CL1 and CL2. If the allocatable hard register sets are

the same, prefer GENERAL_REGS or the

smallest class for debugging

purposes. Ignore unavailable hard registers and prefer

smallest class for debugging purposes. CL3 allocatbale hard register set is inside of

union of allocatable hard register sets of CL1

and CL2. If the allocatable hard register sets are the

same, prefer GENERAL_REGS or the smallest

class for debugging purposes. CL3 allocatable hard register set contains union

of allocatable hard register sets of CL1 and

CL2. If the allocatable hard register sets are the

same, prefer GENERAL_REGS or the smallest

class for debugging purposes.

|

static |

Set up fields memory, constant, and invariant from init_insns in the structures of array ira_reg_equiv.

Init insns can set up equivalence when the reg is a destination or

a source (in this case the destination is memory).

This insn reporting the equivalence but

actually not setting it. Remove it from the

list. A function invariant is often CONSTANT_P but may

include a register. We promise to only pass

CONSTANT_P objects to LEGITIMATE_PIC_OPERAND_P. It can happen that a REG_EQUIV note contains a MEM

that is not a legitimate memory operand. As later

stages of reload assume that all addresses found in

the lra_regno_equiv_* arrays were originally

legitimate, we ignore such REG_EQUIV notes. This is PLUS of frame pointer and a constant,

or fp, or argp.

References bitmap_bit_p, bitmap_clear_bit(), bitmap_empty_p(), bitmap_set_bit, DF_REF_CONDITIONAL, DF_REF_FLAGS_IS_SET, DF_REF_MAY_CLOBBER, DF_REF_PARTIAL, DF_REF_REG, DF_REF_REGNO, DF_REF_STRICT_LOW_PART, DF_REF_ZERO_EXTRACT, fixed_regs, GET_CODE, GET_MODE, GET_MODE_SIZE, init_live_subregs(), ira_conflicts_p, last, pseudo_for_reload_consideration_p(), SBITMAP_SIZE, and SUBREG_BYTE.

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

Allocate REG_EQUIV_INIT. Set up it from IRA_REG_EQUIV which should be already calculated.

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

The function sets up the map IRA_REG_MODE_HARD_REGSET.

|

static |

Set up REG_RENUMBER and CALLER_SAVE_NEEDED (used by reload) from the allocation found by IRA.

There are no caps at this point.

It can happen if A is not referenced but partially anticipated

somewhere in a region.

|

static |

Initialize the table of subclasses of each reg class.

|

static |

Set up ira_stack_reg_pressure_class which is the biggest pressure register class containing stack registers or NO_REGS if there are no stack registers. To find this class, we iterate through all register pressure classes and choose the first register pressure class containing all the stack registers and having the biggest size.

References alloc_reg_class_subclasses, COPY_HARD_REG_SET, HARD_REG_SET, ira_class_hard_regs_num, reg_class_contents, and temp_hard_regset.

|

static |

Set up IRA_UNIFORM_CLASS_P. Uniform class is a register class whose register move cost between any registers of the class is the same as for all its subclasses. We use the data to speed up the 2nd pass of calculations of allocno costs.

We can not use alloc_reg_class_subclasses here because move cost hooks does not take into account that some registers are unavailable for the subtarget. E.g. for i686, INT_SSE_REGS is element of alloc_reg_class_subclasses for GENERAL_REGS because SSE regs are unavailable.

References AND_COMPL_HARD_REG_SET, COPY_HARD_REG_SET, HARD_REG_SET, hard_reg_set_equal_p(), no_unit_alloc_regs, reg_class_contents, and temp_hard_regset.

|

static |

Split live ranges of pseudos that are loaded from hard registers in the first BB in a BB that dominates all non-sibling call if such a BB can be found and is not in a loop. Return true if the function has made any changes.

This is necessary to avoid hitting an assert at postreload.c:2294 in libstc++ testcases on x86_64-linux. I'm not really sure what the probblem actually is there.

References AVOID_CFG_MODIFICATIONS, bitmap_obstack_initialize(), calculate_dominance_info(), CDI_DOMINATORS, cfun, df_d::changeable_flags, crtl, current_loops, decrease_live_ranges_number(), delete_trivially_dead_insns(), delete_unreachable_blocks(), df, df_analyze(), df_clear_flags(), df_live, DF_NO_INSN_RESCAN, df_note_add_problem(), df_remove_problem(), DF_VERIFY_SCHEDULED, FALSE, find_moveable_pseudos(), free_dominance_info(), gcc_checking_assert, gcc_obstack_init, generate_setjmp_warnings(), get_insns(), init_caller_save(), init_reg_equiv(), internal_flag_ira_verbose, ira_additional_jumps_num, ira_assert, ira_bitmap_obstack, ira_build(), ira_color(), ira_dump_file, ira_emit(), ira_initiate_assign(), ira_initiate_emit_data(), ira_load_cost, ira_max_point, ira_mem_cost, ira_move_loops_num, ira_overall_cost, ira_reg_cost, IRA_REGION_ALL, IRA_REGION_MIXED, IRA_REGION_ONE, ira_set_pseudo_classes(), ira_setup_eliminable_regset(), ira_shuffle_cost, ira_store_cost, last_basic_block, leaf_function_p(), loop_optimizer_init(), LOOPS_HAVE_RECORDED_EXITS, lra_simple_p, max_reg_num(), max_regno_before_ira, NULL, purge_all_dead_edges(), rebuild_jump_labels(), regstat_compute_ri(), regstat_init_n_sets_and_refs(), resize_reg_info(), setup_prohibited_mode_move_regs(), setup_reg_equiv(), setup_reg_equiv_init(), targetm, timevar_pop(), timevar_push(), too_high_register_pressure_p(), and update_equiv_regs().

|

static |

Return TRUE if there is too high register pressure in the function. It is used to decide when stack slot sharing is worth to do.

References equiv_mem_modified, find_reg_note(), INSN_P, NEXT_INSN, and side_effects_p().

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

Find registers that are equivalent to a single value throughout the compilation (either because they can be referenced in memory or are set once from a single constant). Lower their priority for a register.

If such a register is only referenced once, try substituting its value into the using insn. If it succeeds, we can eliminate the register completely.

Initialize init_insns in ira_reg_equiv array.

Return non-zero if jump label rebuilding should be done.

We need to keep track of whether or not we recorded a LABEL_REF so that we know if the jump optimizer needs to be rerun.

Use pdx_subregs to show whether a reg is used in a paradoxical subreg.

Scan insns and set pdx_subregs[regno] if the reg is used in a paradoxical subreg. Don't set such reg sequivalent to a mem, because lra will not substitute such equiv memory in order to prevent access beyond allocated memory for paradoxical memory subreg.

Scan the insns and find which registers have equivalences. Do this in a separate scan of the insns because (due to -fcse-follow-jumps) a register can be set below its use.

If this insn contains more (or less) than a single SET,

only mark all destinations as having no known equivalence. See if this is setting up the equivalence between an argument

register and its stack slot. Note that we don't want to clear init_insns in

ira_reg_equiv even if there are multiple sets of this

register. The insn result can have equivalence memory although

the equivalence is not set up by the insn. We add

this insn to init insns as it is a flag for now that

regno has an equivalence. We will remove the insn

from init insn list later. Continue normally in case this is a candidate for

replacements. We only handle the case of a pseudo register being set

once, or always to the same value. ??? The mn10200 port breaks if we add equivalences for

values that need an ADDRESS_REGS register and set them equivalent

to a MEM of a pseudo. The actual problem is in the over-conservative

handling of INPADDR_ADDRESS / INPUT_ADDRESS / INPUT triples in

calculate_needs, but we traditionally work around this problem

here by rejecting equivalences when the destination is in a register

that's likely spilled. This is fragile, of course, since the

preferred class of a pseudo depends on all instructions that set

or use it. This might be setting a SUBREG of a pseudo, a pseudo that is

also set somewhere else to a constant. Don't set reg (if pdx_subregs[regno] == true) equivalent to a mem.

cse sometimes generates function invariants, but doesn't put a

REG_EQUAL note on the insn. Since this note would be redundant,

there's no point creating it earlier than here. Don't bother considering a REG_EQUAL note containing an EXPR_LIST

since it represents a function call Record this insn as initializing this register.

If this register is known to be equal to a constant, record that

it is always equivalent to the constant. If this insn introduces a "constant" register, decrease the priority

of that register. Record this insn if the register is only used once

more and the equivalence value is the same as our source.

The latter condition is checked for two reasons: First, it is an

indication that it may be more efficient to actually emit the insn

as written (if no registers are available, reload will substitute

the equivalence). Secondly, it avoids problems with any registers

dying in this insn whose death notes would be missed.

If we don't have a REG_EQUIV note, see if this insn is loading

a register used only in one basic block from a MEM. If so, and the

MEM remains unchanged for the life of the register, add a REG_EQUIV

note. If we haven't done so, record for reload that this is an

equivalencing insn. Record whether or not we created a REG_EQUIV note for a LABEL_REF.

We might end up substituting the LABEL_REF for uses of the

pseudo here or later. That kind of transformation may turn an

indirect jump into a direct jump, in which case we must rerun the

jump optimizer to ensure that the JUMP_LABEL fields are valid. Don't mess with things live during setjmp.

Note that the statement below does not affect the priority

in local-alloc! If the register is referenced exactly twice, meaning it is

set once and used once, indicate that the reference may be

replaced by the equivalence we computed above. Do this

even if the register is only used in one block so that

dependencies can be handled where the last register is

used in a different block (i.e. HIGH / LO_SUM sequences)

and to reduce the number of registers alive across

calls. A second pass, to gather additional equivalences with memory. This needs to be done after we know which registers we are going to replace.

If this sets a MEM to the contents of a REG that is only used

in a single basic block, see if the register is always equivalent

to that memory location and if moving the store from INSN to the

insn that set REG is safe. If so, put a REG_EQUIV note on the

initializing insn.

Don't add a REG_EQUIV note if the insn already has one. The existing

REG_EQUIV is likely more useful than the one we are adding.

If one of the regs in the address has reg_equiv[REGNO].replace set,

then we can't add this REG_EQUIV note. The reg_equiv[REGNO].replace

optimization may move the set of this register immediately before

insn, which puts it after reg_equiv[REGNO].init_insns, and hence

the mention in the REG_EQUIV note would be to an uninitialized

pseudo. Attaching a REG_EQUIV note will fail if INIT_INSN has

multiple sets. This insn makes the equivalence, not the one initializing

the register. Now scan all regs killed in an insn to see if any of them are registers only used that once. If so, see if we can replace the reference with the equivalent form. If we can, delete the initializing reference and this register will go away. If we can't replace the reference, and the initializing reference is within the same loop (or in an inner loop), then move the register initialization just before the use, so that they are in the same basic block.

Don't substitute into a non-local goto, this confuses CFG.

Make sure this insn still refers to the register.

There is no sense to move insns if we did

register pressure-sensitive scheduling was

done because it will not improve allocation

but worsen insn schedule with a big

probability. reg_equiv[REGNO].replace gets set only when

REG_N_REFS[REGNO] is 2, i.e. the register is set

once and used once. (If it were only set, but

not used, flow would have deleted the setting

insns.) Hence there can only be one insn in

reg_equiv[REGNO].init_insns. We may not move instructions that can throw, since

that changes basic block boundaries and we are not

prepared to adjust the CFG to match. Find the last note.

Append the REG_DEAD notes from equiv_insn.

Move the initialization of the register to just before

INSN. Update the flow information. Rescan it to process the notes.

Make sure this insn is recognized before

reload begins, otherwise

eliminate_regs_in_insn will die. Last pass - adjust debug insns referencing cleared regs.

Clean up.

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

Verify that no store between START and the death of REG invalidates MEMREF. MEMREF is invalidated by modifying a register used in MEMREF, by storing into an overlapping memory location, or with a non-const CALL_INSN.

Return 1 if MEMREF remains valid.

If the memory reference has side effects or is volatile, it isn't a valid equivalence.

This used to ignore readonly memory and const/pure calls. The problem

is the equivalent form may reference a pseudo which gets assigned a

call clobbered hard reg. When we later replace REG with its

equivalent form, the value in the call-clobbered reg has been

changed and all hell breaks loose. If a register mentioned in MEMREF is modified via an

auto-increment, we lose the equivalence. Do the same if one

dies; although we could extend the life, it doesn't seem worth

the trouble.

If EQUIV_MEM is modified by modifying DEST, indicate that it is modified. Called via note_stores.

Variable Documentation

|

static |

The number of entries allocated in teg_info.

|

static |

Order numbers of allocno classes in original target allocno class array, -1 for non-allocno classes.

| struct target_ira default_target_ira |

Integrated Register Allocator (IRA) entry point. Copyright (C) 2006-2013 Free Software Foundation, Inc. Contributed by Vladimir Makarov vmakarov@redhat.com.

This file is part of GCC.

GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version.

GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see http://www.gnu.org/licenses/. The integrated register allocator (IRA) is a regional register allocator performing graph coloring on a top-down traversal of nested regions. Graph coloring in a region is based on Chaitin-Briggs algorithm. It is called integrated because register coalescing, register live range splitting, and choosing a better hard register are done on-the-fly during coloring. Register coalescing and choosing a cheaper hard register is done by hard register preferencing during hard register assigning. The live range splitting is a byproduct of the regional register allocation.

Major IRA notions are:

o Region is a part of CFG where graph coloring based on Chaitin-Briggs algorithm is done. IRA can work on any set of nested CFG regions forming a tree. Currently the regions are the entire function for the root region and natural loops for the other regions. Therefore data structure representing a region is called loop_tree_node.

o Allocno class is a register class used for allocation of given allocno. It means that only hard register of given register class can be assigned to given allocno. In reality, even smaller subset of (profitable) hard registers can be assigned. In rare cases, the subset can be even smaller because our modification of Chaitin-Briggs algorithm requires that sets of hard registers can be assigned to allocnos forms a forest, i.e. the sets can be ordered in a way where any previous set is not intersected with given set or is a superset of given set.

o Pressure class is a register class belonging to a set of register classes containing all of the hard-registers available for register allocation. The set of all pressure classes for a target is defined in the corresponding machine-description file according some criteria. Register pressure is calculated only for pressure classes and it affects some IRA decisions as forming allocation regions.

o Allocno represents the live range of a pseudo-register in a region. Besides the obvious attributes like the corresponding pseudo-register number, allocno class, conflicting allocnos and conflicting hard-registers, there are a few allocno attributes which are important for understanding the allocation algorithm:

- Live ranges. This is a list of ranges of program points where the allocno lives. Program points represent places where a pseudo can be born or become dead (there are approximately two times more program points than the insns) and they are represented by integers starting with 0. The live ranges are used to find conflicts between allocnos. They also play very important role for the transformation of the IRA internal representation of several regions into a one region representation. The later is used during the reload pass work because each allocno represents all of the corresponding pseudo-registers.

Hard-register costs. This is a vector of size equal to the number of available hard-registers of the allocno class. The cost of a callee-clobbered hard-register for an allocno is increased by the cost of save/restore code around the calls through the given allocno's life. If the allocno is a move instruction operand and another operand is a hard-register of the allocno class, the cost of the hard-register is decreased by the move cost.

When an allocno is assigned, the hard-register with minimal full cost is used. Initially, a hard-register's full cost is the corresponding value from the hard-register's cost vector. If the allocno is connected by a copy (see below) to another allocno which has just received a hard-register, the cost of the hard-register is decreased. Before choosing a hard-register for an allocno, the allocno's current costs of the hard-registers are modified by the conflict hard-register costs of all of the conflicting allocnos which are not assigned yet.

- Conflict hard-register costs. This is a vector of the same size as the hard-register costs vector. To permit an unassigned allocno to get a better hard-register, IRA uses this vector to calculate the final full cost of the available hard-registers. Conflict hard-register costs of an unassigned allocno are also changed with a change of the hard-register cost of the allocno when a copy involving the allocno is processed as described above. This is done to show other unassigned allocnos that a given allocno prefers some hard-registers in order to remove the move instruction corresponding to the copy.

o Cap. If a pseudo-register does not live in a region but lives in a nested region, IRA creates a special allocno called a cap in the outer region. A region cap is also created for a subregion cap.

o Copy. Allocnos can be connected by copies. Copies are used to modify hard-register costs for allocnos during coloring. Such modifications reflects a preference to use the same hard-register for the allocnos connected by copies. Usually copies are created for move insns (in this case it results in register coalescing). But IRA also creates copies for operands of an insn which should be assigned to the same hard-register due to constraints in the machine description (it usually results in removing a move generated in reload to satisfy the constraints) and copies referring to the allocno which is the output operand of an instruction and the allocno which is an input operand dying in the instruction (creation of such copies results in less register shuffling). IRA does not create copies between the same register allocnos from different regions because we use another technique for propagating hard-register preference on the borders of regions.

Allocnos (including caps) for the upper region in the region tree accumulate information important for coloring from allocnos with the same pseudo-register from nested regions. This includes hard-register and memory costs, conflicts with hard-registers, allocno conflicts, allocno copies and more. Thus, attributes for allocnos in a region have the same values as if the region had no subregions. It means that attributes for allocnos in the outermost region corresponding to the function have the same values as though the allocation used only one region which is the entire function. It also means that we can look at IRA work as if the first IRA did allocation for all function then it improved the allocation for loops then their subloops and so on.

IRA major passes are:

o Building IRA internal representation which consists of the following subpasses:

First, IRA builds regions and creates allocnos (file ira-build.c) and initializes most of their attributes.

Then IRA finds an allocno class for each allocno and calculates its initial (non-accumulated) cost of memory and each hard-register of its allocno class (file ira-cost.c).

IRA creates live ranges of each allocno, calulates register pressure for each pressure class in each region, sets up conflict hard registers for each allocno and info about calls the allocno lives through (file ira-lives.c).

IRA removes low register pressure loops from the regions mostly to speed IRA up (file ira-build.c).

IRA propagates accumulated allocno info from lower region allocnos to corresponding upper region allocnos (file ira-build.c).

IRA creates all caps (file ira-build.c).

Having live-ranges of allocnos and their classes, IRA creates conflicting allocnos for each allocno. Conflicting allocnos are stored as a bit vector or array of pointers to the conflicting allocnos whatever is more profitable (file ira-conflicts.c). At this point IRA creates allocno copies.

o Coloring. Now IRA has all necessary info to start graph coloring process. It is done in each region on top-down traverse of the region tree (file ira-color.c). There are following subpasses:

Finding profitable hard registers of corresponding allocno class for each allocno. For example, only callee-saved hard registers are frequently profitable for allocnos living through colors. If the profitable hard register set of allocno does not form a tree based on subset relation, we use some approximation to form the tree. This approximation is used to figure out trivial colorability of allocnos. The approximation is a pretty rare case.

Putting allocnos onto the coloring stack. IRA uses Briggs optimistic coloring which is a major improvement over Chaitin's coloring. Therefore IRA does not spill allocnos at this point. There is some freedom in the order of putting allocnos on the stack which can affect the final result of the allocation. IRA uses some heuristics to improve the order.

We also use a modification of Chaitin-Briggs algorithm which works for intersected register classes of allocnos. To figure out trivial colorability of allocnos, the mentioned above tree of hard register sets is used. To get an idea how the algorithm works in i386 example, let us consider an allocno to which any general hard register can be assigned. If the allocno conflicts with eight allocnos to which only EAX register can be assigned, given allocno is still trivially colorable because all conflicting allocnos might be assigned only to EAX and all other general hard registers are still free.

To get an idea of the used trivial colorability criterion, it is also useful to read article "Graph-Coloring Register Allocation for Irregular Architectures" by Michael D. Smith and Glen Holloway. Major difference between the article approach and approach used in IRA is that Smith's approach takes register classes only from machine description and IRA calculate register classes from intermediate code too (e.g. an explicit usage of hard registers in RTL code for parameter passing can result in creation of additional register classes which contain or exclude the hard registers). That makes IRA approach useful for improving coloring even for architectures with regular register files and in fact some benchmarking shows the improvement for regular class architectures is even bigger than for irregular ones. Another difference is that Smith's approach chooses intersection of classes of all insn operands in which a given pseudo occurs. IRA can use bigger classes if it is still more profitable than memory usage.

Popping the allocnos from the stack and assigning them hard registers. If IRA can not assign a hard register to an allocno and the allocno is coalesced, IRA undoes the coalescing and puts the uncoalesced allocnos onto the stack in the hope that some such allocnos will get a hard register separately. If IRA fails to assign hard register or memory is more profitable for it, IRA spills the allocno. IRA assigns the allocno the hard-register with minimal full allocation cost which reflects the cost of usage of the hard-register for the allocno and cost of usage of the hard-register for allocnos conflicting with given allocno.

Chaitin-Briggs coloring assigns as many pseudos as possible to hard registers. After coloringh we try to improve allocation with cost point of view. We improve the allocation by spilling some allocnos and assigning the freed hard registers to other allocnos if it decreases the overall allocation cost.

After allono assigning in the region, IRA modifies the hard register and memory costs for the corresponding allocnos in the subregions to reflect the cost of possible loads, stores, or moves on the border of the region and its subregions. When default regional allocation algorithm is used (-fira-algorithm=mixed), IRA just propagates the assignment for allocnos if the register pressure in the region for the corresponding pressure class is less than number of available hard registers for given pressure class.

o Spill/restore code moving. When IRA performs an allocation by traversing regions in top-down order, it does not know what happens below in the region tree. Therefore, sometimes IRA misses opportunities to perform a better allocation. A simple optimization tries to improve allocation in a region having subregions and containing in another region. If the corresponding allocnos in the subregion are spilled, it spills the region allocno if it is profitable. The optimization implements a simple iterative algorithm performing profitable transformations while they are still possible. It is fast in practice, so there is no real need for a better time complexity algorithm.

o Code change. After coloring, two allocnos representing the same pseudo-register outside and inside a region respectively may be assigned to different locations (hard-registers or memory). In this case IRA creates and uses a new pseudo-register inside the region and adds code to move allocno values on the region's borders. This is done during top-down traversal of the regions (file ira-emit.c). In some complicated cases IRA can create a new allocno to move allocno values (e.g. when a swap of values stored in two hard-registers is needed). At this stage, the new allocno is marked as spilled. IRA still creates the pseudo-register and the moves on the region borders even when both allocnos were assigned to the same hard-register. If the reload pass spills a pseudo-register for some reason, the effect will be smaller because another allocno will still be in the hard-register. In most cases, this is better then spilling both allocnos. If reload does not change the allocation for the two pseudo-registers, the trivial move will be removed by post-reload optimizations. IRA does not generate moves for allocnos assigned to the same hard register when the default regional allocation algorithm is used and the register pressure in the region for the corresponding pressure class is less than number of available hard registers for given pressure class. IRA also does some optimizations to remove redundant stores and to reduce code duplication on the region borders.

o Flattening internal representation. After changing code, IRA transforms its internal representation for several regions into one region representation (file ira-build.c). This process is called IR flattening. Such process is more complicated than IR rebuilding would be, but is much faster.

o After IR flattening, IRA tries to assign hard registers to all spilled allocnos. This is impelemented by a simple and fast priority coloring algorithm (see function ira_reassign_conflict_allocnos::ira-color.c). Here new allocnos created during the code change pass can be assigned to hard registers.

o At the end IRA calls the reload pass. The reload pass communicates with IRA through several functions in file ira-color.c to improve its decisions in

sharing stack slots for the spilled pseudos based on IRA info about pseudo-register conflicts.

reassigning hard-registers to all spilled pseudos at the end of each reload iteration.

choosing a better hard-register to spill based on IRA info about pseudo-register live ranges and the register pressure in places where the pseudo-register lives.

IRA uses a lot of data representing the target processors. These data are initilized in file ira.c.

If function has no loops (or the loops are ignored when -fira-algorithm=CB is used), we have classic Chaitin-Briggs coloring (only instead of separate pass of coalescing, we use hard register preferencing). In such case, IRA works much faster because many things are not made (like IR flattening, the spill/restore optimization, and the code change).

Literature is worth to read for better understanding the code:

o Preston Briggs, Keith D. Cooper, Linda Torczon. Improvements to Graph Coloring Register Allocation.

o David Callahan, Brian Koblenz. Register allocation via hierarchical graph coloring.

o Keith Cooper, Anshuman Dasgupta, Jason Eckhardt. Revisiting Graph Coloring Register Allocation: A Study of the Chaitin-Briggs and Callahan-Koblenz Algorithms.

o Guei-Yuan Lueh, Thomas Gross, and Ali-Reza Adl-Tabatabai. Global Register Allocation Based on Graph Fusion.

o Michael D. Smith and Glenn Holloway. Graph-Coloring Register Allocation for Irregular Architectures

o Vladimir Makarov. The Integrated Register Allocator for GCC.

o Vladimir Makarov. The top-down register allocator for irregular register file architectures.

| struct target_ira_int default_target_ira_int |

| HARD_REG_SET eliminable_regset |

All registers that can be eliminated.

Referenced by find_call_crossed_cheap_reg(), insn_contains_asm(), insn_contains_asm_1(), and substitute_pseudo().

|

static |

Used for communication between the following two functions: contains a MEM that we wish to ensure remains unchanged.

|

static |

Set nonzero if EQUIV_MEM is modified.

Referenced by too_high_register_pressure_p().

| int first_moveable_pseudo |

Record the range of register numbers added by find_moveable_pseudos.

| int internal_flag_ira_verbose |

A modified value of flag `-fira-verbose' used internally.

Referenced by allocno_cost_compare_func(), bucket_allocno_compare_func(), build_conflict_bit_table(), collect_spilled_coalesced_allocnos(), ira_debug_live_range_list(), modify_move_list(), move_unallocated_pseudos(), process_bb_node_lives(), push_only_colorable(), and split_live_ranges_for_shrink_wrap().

| int ira_additional_jumps_num |

Referenced by split_live_ranges_for_shrink_wrap().

|

static |

Obstack used for storing all bitmaps of the IRA.

Referenced by split_live_ranges_for_shrink_wrap().

| bool ira_conflicts_p |

True if we have allocno conflicts. It is false for non-optimized mode or when the conflict table is too big.

Referenced by maybe_fix_stack_asms(), print_conflicts(), and setup_reg_equiv().

| FILE* ira_dump_file |

Dump file of the allocator if it is not NULL.

Referenced by allocno_cost_compare_func(), bucket_allocno_compare_func(), build_conflict_bit_table(), collect_spilled_coalesced_allocnos(), ira_debug_live_range_list(), ira_loop_edge_freq(), modify_move_list(), move_unallocated_pseudos(), print_object_live_ranges(), process_bb_node_lives(), push_only_colorable(), and split_live_ranges_for_shrink_wrap().

| int ira_load_cost |

Referenced by emit_move_list(), and split_live_ranges_for_shrink_wrap().

| int ira_mem_cost |

Referenced by split_live_ranges_for_shrink_wrap().

| int ira_move_loops_num |

Referenced by modify_move_list(), and split_live_ranges_for_shrink_wrap().

| int ira_overall_cost |

Correspondingly overall cost of the allocation, overall cost before reload, cost of the allocnos assigned to hard-registers, cost of the allocnos assigned to memory, cost of loads, stores and register move insns generated for pseudo-register live range splitting (see ira-emit.c).

Referenced by split_live_ranges_for_shrink_wrap().

| int ira_reg_cost |

Referenced by split_live_ranges_for_shrink_wrap().

| struct ira_reg_equiv* ira_reg_equiv |

Info about equiv. info for each register.

| int ira_reg_equiv_len |

The length of the following array.

| int ira_shuffle_cost |

Referenced by split_live_ranges_for_shrink_wrap().

| struct ira_spilled_reg_stack_slot* ira_spilled_reg_stack_slots |

The following array contains info about spilled pseudo-registers stack slots used in current function so far.

| int ira_spilled_reg_stack_slots_num |

The number of elements in the following array.

| int ira_store_cost |

Referenced by split_live_ranges_for_shrink_wrap().

| bool ira_use_lra_p |

True when we use LRA instead of reload pass for the current function.

| int last_moveable_pseudo |

|

static |

Value of max_reg_num () before IRA work start. This value helps us to recognize a situation when new pseudos were created during IRA work.

Referenced by move_unallocated_pseudos(), and split_live_ranges_for_shrink_wrap().

| int overall_cost_before |

These two vectors hold data for every register added by find_movable_pseudos, with index 0 holding data for the first_moveable_pseudo. The original home register.

|

static |

Nonzero if we recorded an equivalence for a LABEL_REF.

|

static |

reg_equiv[N] (where N is a pseudo reg number) is the equivalence structure for that register.

| short* reg_renumber |

Vector of substitutions of register numbers, used to map pseudo regs into hardware regs. This is set up as a result of register allocation. Element N is the hard reg assigned to pseudo reg N, or is -1 if no hard reg was assigned. If N is a hard reg number, element N is N.

Referenced by add_to_inherit(), can_reload_into(), check_and_process_move(), init_lives(), insert_save(), invert_exp_1(), invert_jump_1(), ira_reassign_pseudos(), lra_debug_live_ranges(), maybe_fix_stack_asms(), save_call_clobbered_regs(), set_label_offsets(), setup_try_hard_regno_pseudos(), slot_coalesced_allocno_live_ranges_intersect_p(), substitute_pseudo(), and update_hard_regno_preference().

|

static |

Saved between IRA and reload.

|

static |

Temporary hard reg set used for a different calculation.

Referenced by find_reg_classes(), ira_debug_disposition(), setup_allocno_and_important_classes(), setup_hard_regno_aclass(), setup_stack_reg_pressure_class(), and setup_uniform_class_p().